| Zurück |

(C) Christof Ermer, Regensburg |

|

|

08.02.2024 |

TTL ICs

Logik Familien

Inhalt:

TTL-Logik

CMOS-Logik

Kombination

unterschiedlicher

Logikfamilien

Elektromagnetische

Störungen

Anwendungskriterien

Typenauflistung

TTL -Logik

Transitor-Transistor Logik.

Der Eingang eines Standard TTL-Gatters Type 7400 wird durch

den

Emitter eines Transitors gebildet. Dieser steuert die Basis einer

Vorverstärkerstufe

an. Den Ausgang bildet immer eine Gegentaktenstufe. In der

Datenbuchliteratur

als sogenannte Totem-Pole-Endstufe bezeichnet.

Wegen der Sättigungseffekte der Transistoren zu vermeiden wurde

die TTL Transistorschaltstufen mit Schottky-Dioden versehen. Die

Schaltungen

eines Low Power Schottky (LS) TTL-Gatters hat etwa 1/5 der

Verlustleistung

eines Standard-TTL Gatters bei etwa gleicher Gatterlaufzeit.

Weiterentwicklung

der LS- ist die ALS-Technologie mit nochmals verbesserter

Verlustleistung

und niedrigerer Gatterlaufzeit.

Vergleich der TTL-Logik Typen

|

Type

|

74 00

|

74 S 00

|

74 AS 00

|

74 LS 00

|

74 ALS 00

|

74 F 00

|

|

Gatterlaufzeit

|

10 ns

|

4 ns

|

1,5 ns

|

10 ns

|

4 ns

|

3 ns

|

|

Versorgungs-

spannung

|

4,75V..5,25V

|

4,75V..5,25V

|

4,5V..5,5V

|

4,75V..5,25V

|

4,5V..5,5V

|

4,5V..5,5V

|

|

Verlustlaufnahme

pro Gatter

|

10 mW

|

19 mW

|

6 mW

|

2 mW

|

2 mW

|

5 mW

|

Ausgangsstrom

typ. High/Low |

-0,4mA/16mA |

-1mA/20mA |

|

-0,4mA/8mA |

0,4mA/4mA |

-1mA/20mA |

Eingangsstrom

typ. High/Low |

40uA/-1,6mA |

|

|

20mA/-0,36mA |

20uA/-0,2mA |

|

Tabelle 1

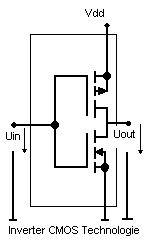

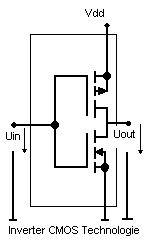

CMOS -Logik

Complementary (Komplementär-) Metalic Oxid Semiconductor Logik.

Schaltkreise

sind ausschließlich aus selbstsperrenden Mosfets aufgebaut.Ein

CMOS-Gatter

reagiert äußerst empfindlich auf Eingangsspannungen (Uin),

welche

über der Versorgungspannung (Vdd), oder unter dem

0V-Versorgungspotential

liegen. Dadurch schließt nämlich der Schaltkreis im ungünstigsten

Fall intern die Versorgungsspannung kurz und lebt ab.

Schaltkreise

sind ausschließlich aus selbstsperrenden Mosfets aufgebaut.Ein

CMOS-Gatter

reagiert äußerst empfindlich auf Eingangsspannungen (Uin),

welche

über der Versorgungspannung (Vdd), oder unter dem

0V-Versorgungspotential

liegen. Dadurch schließt nämlich der Schaltkreis im ungünstigsten

Fall intern die Versorgungsspannung kurz und lebt ab.

Technologischer Vergleich

| Technologie |

Silicon-Gate Type

74HC00 |

Metal-Gate Type

C4001 |

Gatterlaufzeit

typ.

(bei Vdd=5V) |

10 ns |

90 ns |

| Versorgungsspannung |

3V...6V |

3V...15V |

| Verlustleistung |

0,4 uW/kHz |

0,3 uW/kHz |

Tabelle2

Vergleich der CMOS-Logik Typen

| Type |

74

HC/HCT 00 |

74

AHC/AHCT 00 |

74

AC/ACT 00 |

74

LV/LVT |

74

FCT240CT |

74

BCT240 |

Gatterlaufzeit

max. |

23 ns |

6,5 ns |

4,4 ns |

6ns |

4,7 ns |

9 ns |

Ausgangsstrom

|

+/-4mA |

+/-8mA |

+/-24mA |

+/-12mA(2,7V)

+/-24mA(3V) |

-15/+64mA |

-15/+64mA |

|

Versorgungs-

spannung |

4,5V..5,5V(HCT)

2V...6V(HC) |

4,5V..5,5V(HCT)

2V...5,5V(HC) |

4,5V..5,5V(ACT)

2V...6V(AC) |

2V..3,6V |

4,5V..5,5V |

4,5V..5,5V |

typ. stat.

Stromaufnahme |

65uA |

40uA |

20uA |

10uA |

0,8mA |

6 mA |

| Hersteller |

TI, |

TI, |

TI, |

TI |

IDT,Harris,Nat |

TI, |

Tabelle 3

Kombination

unterschiedlicher

Logikfamilien

Wer kann mit wem? Die Frage liegt einem auf der Zunge, bei all der

Auswahl.

Solange man in der Sippe bleibt können nur Probleme auftreten, wenn

die zulässige Anzahl an Lastgattern am Ausgang überschritten

wird (Fan Out). Ein- und Ausgangspegel harmonieren.

Dieser Rahmen würde gesprengt, würde ich versuche alle auf

dieser Seite aufgelistete Logik mit einander verheiraten wollen. Ich

beschränke

mich deshalb auf die momentan in der Laborarbeit wichtigsten Familien.

Dies ist aus der Familie TTL der 74LSxx bzw. 74ALSxx und aus der

Familie

derer von CMOS die 74HC/HCTxx bzw. 74AC/ACTxx Bausteine.

Um Logik unterschiedlicher Familien miteinander verheiraten zu können

sind die Spannungpegel, welche die "logische 0" (low) oder "logische 1"

(High) repräsentieren, entscheidend.

Innerhalb der TTL-Familie gibt es keine Bedenken, Logik zu kombinieren.

Der Übergang von TTL-Logik nach CMOS Logik sollte zunächst zur

Logikpegelanpassung mit 74HCTxx-Gattern geschehen. Danach kann in

reiner

CMOS-Technik 74HCxx

"weitergefahren" werden.

Welche Pegel sind dazu zubeachten. Um einen sicheren Störabstand

zu gewinnen, gilt für die Spannungen (V) eines verbundenes

Aus-/Eingangs-

Paares (Output/Input):

| Output-Low VOL |

< |

Input-Low VIL |

| Output-High VOH |

> |

Input-High VIH |

Tabelle4

Für die Ein-/Ausgangs-Pegel gilt:

|

74LSxx (5V) |

74ALSxx (5V) |

|

74HCTxx (5V) |

74HCxx (5V) |

74HCxx (2V) |

| VOH [V]

min |

2,7 |

2,7 |

|

4,5 |

4,5 |

2,0 |

| VOL [V]

max |

0,5 |

0,5 |

|

0,25 |

0,25 |

0,26 |

| VIH [V]

min |

2,0 |

2,0 |

|

2,0 |

3,5 |

1,5 |

| VIL [V]

max |

0,8 |

0,8 |

|

0,8 |

1,5 |

0,5 |

Tabelle5

Ein 74LSxx oder 74ALSxx durch ein CMOS Gatter anzusteuern, stellt wie

aus

Tabelle2 ersichtlich kein Problem dar. Beachten sie aber der Fan out

eines

CMOS Gatters bei der Ansteuerung mehrerer TTL-Gatter. Beachten sie in

Tabelle

1, dass ein Ansteuern eines TTL-Gatters mit einem Low-Pegel bedeutet,

dass

ein Strom aus dem Eingang gezogen wird. Er ist deshalb mit "-"

bezeichnet.

Ein Ansteuern mit einem High-Pegel bewirkt, dass ein Strom in den

Gattereingang

fließen muss, dieser ist mit einem positiven Vorzeichen (Tabelle

1) versehen. Bei den CMOS-Gattern sind die Eingangsströme

vernachlässigbar

klein.

Fan Out ,

die Belastbarkeit eines Ausgangs

Um den Entwickler die Konstruktionsleben einfacher zu

gestalten,

wurde eine rechnerische Größe, der sogenannte fan-out

eines Gatters festgelegt. Dieser kann errechnet oder dem

TTL-Datenbüchern

entnommen werden. Der fan out ist die normierte Belastbarkeit eines

Gatters,

er gibt an, wieviele Gatter einer Logikfamilie, ein Ausgang sicher

ansteuern

kann. Ein fan-out von 20 sagt dem zu Folge, dass dieses Gatter 20

Eingänge

dieser bestimmten Logikserie treiben kann. Die Tabelle 6 zeigt für

ein Gatter der LS-Serie die Berechnung des fan out.

| log. Ausgangspegel |

Ausgangsstrom |

Eingangsstrom |

Fan OUT |

| 1 (min 2,4V) |

-0,4mA |

20mA |

20 |

| 0 (max 0,4) |

8 mA |

-0,36mA |

20 (22,2) |

Tabelle 6

Elektromagnetische

Störungen

Das Thema "Störung in digitalen Schaltungen" an dieser Stelle

verbindlich

und erschöpfend zu behandeln, wäre anmassend. Es gibt aber einige

Designgrundregeln, die ein Leben "mit der Störung möglich" machen.

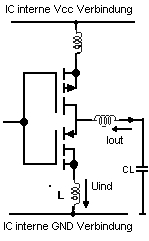

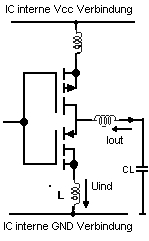

1. Störeffekte durch den Halbleiter-Chip

Zum einem sorgt Totem-Pole der TTL-Familie, als auch die die

Gegentaktendstufe der CMOS-Gatter sorgt mit steigender Schaltfrequenzen

für steigende Störströme auf den Versorgungsleitungen der

Schaltkreise.

Zum anderen existiert für die TTL-Familie ein ungleiches Verhältnis

der Eingangsströme bei Ansteuerung mit High(IIH)

bzw. Low-Pegel ( IIL).

Tabelle 6 zeigt die Eingangsströme

von 3 ausgewählten TTL-Serien.

Zum dritten sorgt die Halbleiterphysik (Transistoraufbau, kapazitive

u. induktivitäte Störeffekte, Bonding des Chips ) für die

sogenannten Ground Bounce Effekte.

Einfluß der Ausgangsstufen:

Betrachten wir zunächst der Einfluss der Ausgangsstufe auf die

Versorgungsspannung.

Die Eingangsstufen:

Die zweite oben genannte Störfaktor liegt im physsikalischen Verhalten

der Eingangsstufe

| Ströme /Serie |

74Sxx |

74LSxx |

74Fxx |

| Eingangsstrom High IIH |

50uA |

20uA |

|

| Eingangsstrom Low IIL |

-2mA |

-0,4mA |

|

Tabelle6

Wie ersichtlich, ändern sich z.B. für 74LSxx-Serie die Eingangsströme

im Verhältnis (IIL:IIH) 1:

20 pro angeschlossenen Gattereingang. Für die CMOS-Familie

ist

das Verhältnis (IIL:IIH) annäherd

1:1, dafür sind die die Ausgangsstufen im Umschaltzeitpunkt stark

kapazitiv durch die anzusteuernden CMOS-Eingänge belastet.

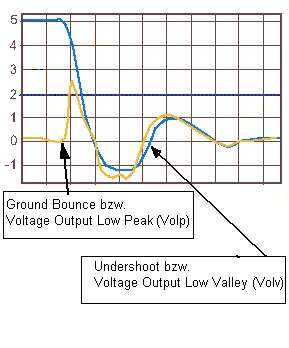

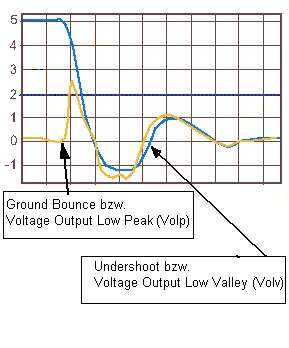

Ground-Bouncing und Undershoot

Der Begriff

to bounce (engl. hochspringen, hochschnellen)

meint, dass an der

parasitären Induktivität zur GND-Verbindung eines Schaltkreises

eine Spannung während Transistion von z..B. High

nach

Low Pegel induziert wird. Ein intern oder extern

weiterführtes

Signals, welches derart beeinflußt worden ist, kann natürlich

mit hoher Wahrscheinlichkeit zu Fehlfunktionen des gesamten Designs

führen.

Der Begriff

to bounce (engl. hochspringen, hochschnellen)

meint, dass an der

parasitären Induktivität zur GND-Verbindung eines Schaltkreises

eine Spannung während Transistion von z..B. High

nach

Low Pegel induziert wird. Ein intern oder extern

weiterführtes

Signals, welches derart beeinflußt worden ist, kann natürlich

mit hoher Wahrscheinlichkeit zu Fehlfunktionen des gesamten Designs

führen.

Die Größe des Spannungshubs, oder Volp (Voltage Output High)

ergibt sich angenähert aus der Gleichung Uind = L di/dt.

Je größer der Schaltstrom und je kürzer der Schaltzeitraum,

desto größer wird die induzierte Spannung ausfallen. Vorallem

beim Entwurf mit schneller CMOS-Logik, mit kürzesten Umschaltzeiten

und großen Lasten, treten diese Probleme auf. Bedeutsam ist in diesem

Zusammenhang auch die Anzahl der gleichzeitig schaltenden Ausgänge.

.

Der sogenannte

Undershoot hängt von den Lastverhältnissen am Ausgang des Gatters

ab. Parameter ist die kapazitive Belastung CL,

die

parasitäre Induktivität L und einer Wirklast R. Der Undershoot

reduziert sich, wenn die kapazitive Last an einem Ausgang erhöht,

oder die Induktivität am Ausgang verringert wird. In einem Design

treten dehalb auf einem stark belasteten Bus eine geringe Störung

durch overshoots auf, als wenn ein schnelles CMOS-Gatter nur mehrere

CMOS-Eingänge

zu treiben hat. Moderne schnelle CMOS-Bausteine besitzen spezielle

Undershoot

Filterschaltungen oder zusätzliche Transistoren die den Ground Bounce

Effekt minimieren helfen.

Der sogenannte

Undershoot hängt von den Lastverhältnissen am Ausgang des Gatters

ab. Parameter ist die kapazitive Belastung CL,

die

parasitäre Induktivität L und einer Wirklast R. Der Undershoot

reduziert sich, wenn die kapazitive Last an einem Ausgang erhöht,

oder die Induktivität am Ausgang verringert wird. In einem Design

treten dehalb auf einem stark belasteten Bus eine geringe Störung

durch overshoots auf, als wenn ein schnelles CMOS-Gatter nur mehrere

CMOS-Eingänge

zu treiben hat. Moderne schnelle CMOS-Bausteine besitzen spezielle

Undershoot

Filterschaltungen oder zusätzliche Transistoren die den Ground Bounce

Effekt minimieren helfen.

Äußerlich sichtbare Merkmale optimierter schneller CMOS-Schaltkreise

ist das sogenannter Center Pinout. Optimierte GND- und VDD-Verbindungen

sollen im Gehäuse parasitäre Induktivitäten minimieren helfen.

2. Störungen durch das Leiterplatten-Design

Anwendungskriterien

"Es kommt halt' auf die Anwendung an.Und der Kostenrahmen darf auch

nicht

vergessen werden."

So, oder so ähnlich muss eine generelle Antwort auf obige Fragen

lauten.

Deshalb kann folgende Checkliste einen Anhalt geben.

Prüfen Sie, ....

--.....ob die Spannungsversorgungs besonders niedrige

Verlustleistungen

fordert

(z.B.) bei batteriebetriebenen

Geräten

--.....ob die Versorgungspannung Störanteile enthält und

der Spannungspegel in gewissen

Grenzen schwankt.

--.....welche Lasten die Gatter zu treiben haben.

--.....in Dekoderschaltungen, ob die Gatterlaufzeit (z.B. Adressdekoder

zur Speicherauswahl)

ausreichend klein sind (worst

case timing).

--.....ob an Registern (z.B. 74xx574) und Latches (z.B. 74xx573) die

Setup- und

die Hold-Zeiten eingehalten

wird.

--.....ob Sie TTL-kompatible Eingänge benötigen.

--.....ob sich eventuell durch PLD-Einsatz die Gatteranzahl minimieren

lässt,

(beachten Sie dabei, dass

PLD meist ungleich höhere Verlustleistungen haben)

--.....beachten Sie die Störeinflüsse der "steilflankig schaltende"

CMOS-Logik.

(Vorteilhafter Einsatz von

Multilayern, oder mindest kammförmige

Versorgungsleiterbahnführung

bei zweiseitigen Leiterplatten)

--.....ihren vorgegebenen Kostenrahmen.

Typenauflistung

74AC/ACTxx

Advanced High Speed CMOS Logik.

Weiterentwickelte High-Speed CMOS Familie bezüglich statischer

Stromaufnahme und Gatterlaufzeit .Dadurch werden

Signallaufgeschwindigkeit

wie bei bipolaren Logikgattern erreicht. Logik und Oktale Funktionen

(74AC/ACT00

...640) im standisierten Corner-Pinning

Gehäuse (für DIL-Gehäuse: Vdd an rechter oberer, GND

an linker unterer Gehäuseecke).

Die Familie wurde um Bausteine mit Center-Pinning (für DIL-Gehäuse:Vdd

mittig rechts und GND mittig links) erweitert. Dieses Pinout reduziert

die induktiven (z.B. kürzere Bonddrähte) Einflüsse des Gehäuses

(Ground Bouncing Effect). Um in einer Applikationen Störsignale (z.B.

ausgelöst durch Schalt-Spikes auf der Versorgung) zu minimieren, ist

der Einsatz von Center-Pinning-Schaltkreise unbedingt empfohlen.

Die Bausteine werden im TSSOP

und

SSOP

Gehäuse angeboten.

Eigenschaften:

Ausgangsstrom: -12/12mA

Gatterlaufzeit: typ. 3ns max. max 7ns

Verlustleistung in Ruhe (stand-by): 40mW

Verfügbare Gattertypen: Kombinatorik Gatter, FlipFlop, 8-Bit Bausteine

(Oktale)

Widebus (16-Bit)

siehe auch CMOS-Logik

74AHC/AHCTxx

Advanced High Speed CMOS Logik. Typenbezeichnug 74AHCTxx.

Weiterentwickelte High-Speed CMOS Familie bezüglich statischer

Stromaufnahme und Gatterlaufzeit von Texas Instruments. Die Eingänge

sind TTL-kompatibel.

Eigenschaften:

Gatterlaufzeit der 8fach-Bausteine 5,2ns (ca. 3 mal schneller als

74HC/HCT)

Leistungsaufnahme im Standby ca. 40uA (ca. 50% weniger als

74HC/HCT)

Eigenschaften:

Ausgangsstrom: -8/8mA

Gatterlaufzeit : typ. 5,2ns max. 9 ns

Verlustleistung in Ruhe (stand-by): 40mW

Verfügbare Gattertypen: Kombinatorik Gatter, FlipFlop, 8-Bit Bausteine

(Oktale)

siehe auch CMOS-Logik

74ASxx

Advanced Schottky

Eigenschaften:

Ausgangsstrom: -15/64mA

Gatterlaufzeit : max. 6,2 ns

Stromaufnahme: 59mA

Verfügbare Gattertypen: Kombinatorik Gatter, FlipFlop, 8-Bit Bausteine

(Oktale)

siehe auch TTL-Logik

74ALSxx

Advanced Low Power Schottky

Eigenschaften:

Ausgangsstrom: -15/64mA

Gatterlaufzeit : max. 10 ns

Stromaufnahme: 50mA

Verfügbare Gattertypen: Kombinatorik Gatter, FlipFlop, 8-Bit Bausteine

(Oktale)

siehe auch TTL-Logik

74BCTxx/ABTxx

Bus Interface Logic. Spektrum auf Oktal-Typen (Buslogic) beschränkt

. Vergleichbar mit 74FTCxx.

Bipolar Output High Speed CMOS Logik. Typenbezeichnug 74BCTxx.

Weiterentwickelte High-Speed CMOS Bustreiber Familie von

Texas

Instruments. TTL-kompatible CMOS Eingänge kombiniert mit hoher

Treiberausgangsleistung

durch bipolare Ausgangsstufen.

Verfügbare Standardtypen u.a. als 74BCT240..245

oder

74BCT573..574 .

Arbeits-Frequenzbereich 25- bis 30 Mhz.

Hohe Ausgangstreiberleistung Versionen in 24mA bzw. 64mA

Ausgangsstrom: -15/64mA

Eigenschaften (ABT):

Ausgangsstrom: -32/64mA

Gatterlaufzeit : max. 3 ns

Verlustleistung in Ruhe (stand-by): 250mW(Tristate)/30mA(Biploar

Output on)

Verfügbare Gattertypen: 8-Bit Bausteine (Oktale)

siehe auch CMOS-Logik

4xxx CMOS

CMOS Logic Familie der 1.Generation. Typenbezeichnug CD4xxx.

Großer Versorgungsspannung-Bereich von 5 bis 15V. Gegenüber

der HC/HCT-Famile vergleichweise langsam. In der Praxis sehr

empfindlich

gegenüber elektrostatischen Einflüßen.

Hersteller u.a.: Motorola mit eignen Entwicklungen, welche mit CD45xx

bezeichnet werden.

Phillips HEF4xxx

Siehe auch CMOS-Logik

74HC/HCTxx

High Speed CMOS Logik. Typenbezeichnug 74HC/74HCTxx. Historisch

gesehen,

stellt diese Serie die erste Weiterentwicklung der 4000er CMOS Familie

dar. Dabei sind die Vorteile der sehr niedrigen statischen

Verlustleisung

mit Schaltgeschwindigkeiten vergleichbar mit denen der TTL-Familie

gepaart.

Es sind alle gängigen kombinatorischen, Counter und oktale Gatter

(8-Bit Busgatter) verfügbar. Allerdings liegen die zulässigen

Ausgangsströme der Oktalen ca. um Faktor 4 unter denen vergleichbarer

TTL-Bustreiber.

Eigenschaften:

Ausgangsstrom: -8/8mA

Gatterlaufzeit : typ. 11ns max. 20 ns

Stromaufnahme: 80mA

Verfügbare Gattertypen: Kombinatorik Gatter, FlipFlop, 8-Bit Bausteine

(Oktale)

Siehe auch CMOS-Logik

74Fxx

Fast Logic

Gegenüber der der Standard 74xx und 74LSxx Serie wurde durch

Schaltungsmaßnahmen

die Ausgangstreiberleistung erhöht und die Schwellenspannung des

Eingangs

auf etwa 1,5V angehoben.

Dies erhöht den Störabstand der Signale. Vorteilhaft ist,

dass Schwankungen, sowohl der Versorgungsspannung (Vcc) als auch der

Umgebungstemperatur

wesentlich geringen Einfluss auf das Schaltverhalten haben, als bei

anderen

Mitglieder der TTL-Familie.

Eigenschaften:

Ausgangsstrom: -15/64mA

Gatterlaufzeit : max. 6,2 ns

Stromaufnahme: 80mA

Verfügbare Gattertypen: Kombinatorik Gatter, FlipFlop, 8-Bit Bausteine

(Oktale)

siehe auch TTL-Logik

74FCTxx

Fast CMOS Logik. Vergleichbar mit 74BCTxx.

Sehr schnelle CMOS-Logik. Spektrum auf Oktal-Typen (Buslogic)

beschränkt.

Laut Hersteller ein direkter Ersatz für 74Fxx und Am29000.

Hersteller u.a. Harris IDT.

siehe auch CMOS-Logik

74LSxx

Low Power Schottky

siehe auch TTL-Logik

W.Spieß, 2/98

Schaltkreise

sind ausschließlich aus selbstsperrenden Mosfets aufgebaut.Ein

CMOS-Gatter

reagiert äußerst empfindlich auf Eingangsspannungen (Uin),

welche

über der Versorgungspannung (Vdd), oder unter dem

0V-Versorgungspotential

liegen. Dadurch schließt nämlich der Schaltkreis im ungünstigsten

Fall intern die Versorgungsspannung kurz und lebt ab.

Schaltkreise

sind ausschließlich aus selbstsperrenden Mosfets aufgebaut.Ein

CMOS-Gatter

reagiert äußerst empfindlich auf Eingangsspannungen (Uin),

welche

über der Versorgungspannung (Vdd), oder unter dem

0V-Versorgungspotential

liegen. Dadurch schließt nämlich der Schaltkreis im ungünstigsten

Fall intern die Versorgungsspannung kurz und lebt ab.

Der Begriff

to bounce (engl. hochspringen, hochschnellen)

meint, dass an der

parasitären Induktivität zur GND-Verbindung eines Schaltkreises

eine Spannung während Transistion von z..B. High

nach

Low Pegel induziert wird. Ein intern oder extern

weiterführtes

Signals, welches derart beeinflußt worden ist, kann natürlich

mit hoher Wahrscheinlichkeit zu Fehlfunktionen des gesamten Designs

führen.

Der Begriff

to bounce (engl. hochspringen, hochschnellen)

meint, dass an der

parasitären Induktivität zur GND-Verbindung eines Schaltkreises

eine Spannung während Transistion von z..B. High

nach

Low Pegel induziert wird. Ein intern oder extern

weiterführtes

Signals, welches derart beeinflußt worden ist, kann natürlich

mit hoher Wahrscheinlichkeit zu Fehlfunktionen des gesamten Designs

führen.

Der sogenannte

Undershoot hängt von den Lastverhältnissen am Ausgang des Gatters

ab. Parameter ist die kapazitive Belastung CL,

die

parasitäre Induktivität L und einer Wirklast R. Der Undershoot

reduziert sich, wenn die kapazitive Last an einem Ausgang erhöht,

oder die Induktivität am Ausgang verringert wird. In einem Design

treten dehalb auf einem stark belasteten Bus eine geringe Störung

durch overshoots auf, als wenn ein schnelles CMOS-Gatter nur mehrere

CMOS-Eingänge

zu treiben hat. Moderne schnelle CMOS-Bausteine besitzen spezielle

Undershoot

Filterschaltungen oder zusätzliche Transistoren die den Ground Bounce

Effekt minimieren helfen.

Der sogenannte

Undershoot hängt von den Lastverhältnissen am Ausgang des Gatters

ab. Parameter ist die kapazitive Belastung CL,

die

parasitäre Induktivität L und einer Wirklast R. Der Undershoot

reduziert sich, wenn die kapazitive Last an einem Ausgang erhöht,

oder die Induktivität am Ausgang verringert wird. In einem Design

treten dehalb auf einem stark belasteten Bus eine geringe Störung

durch overshoots auf, als wenn ein schnelles CMOS-Gatter nur mehrere

CMOS-Eingänge

zu treiben hat. Moderne schnelle CMOS-Bausteine besitzen spezielle

Undershoot

Filterschaltungen oder zusätzliche Transistoren die den Ground Bounce

Effekt minimieren helfen.